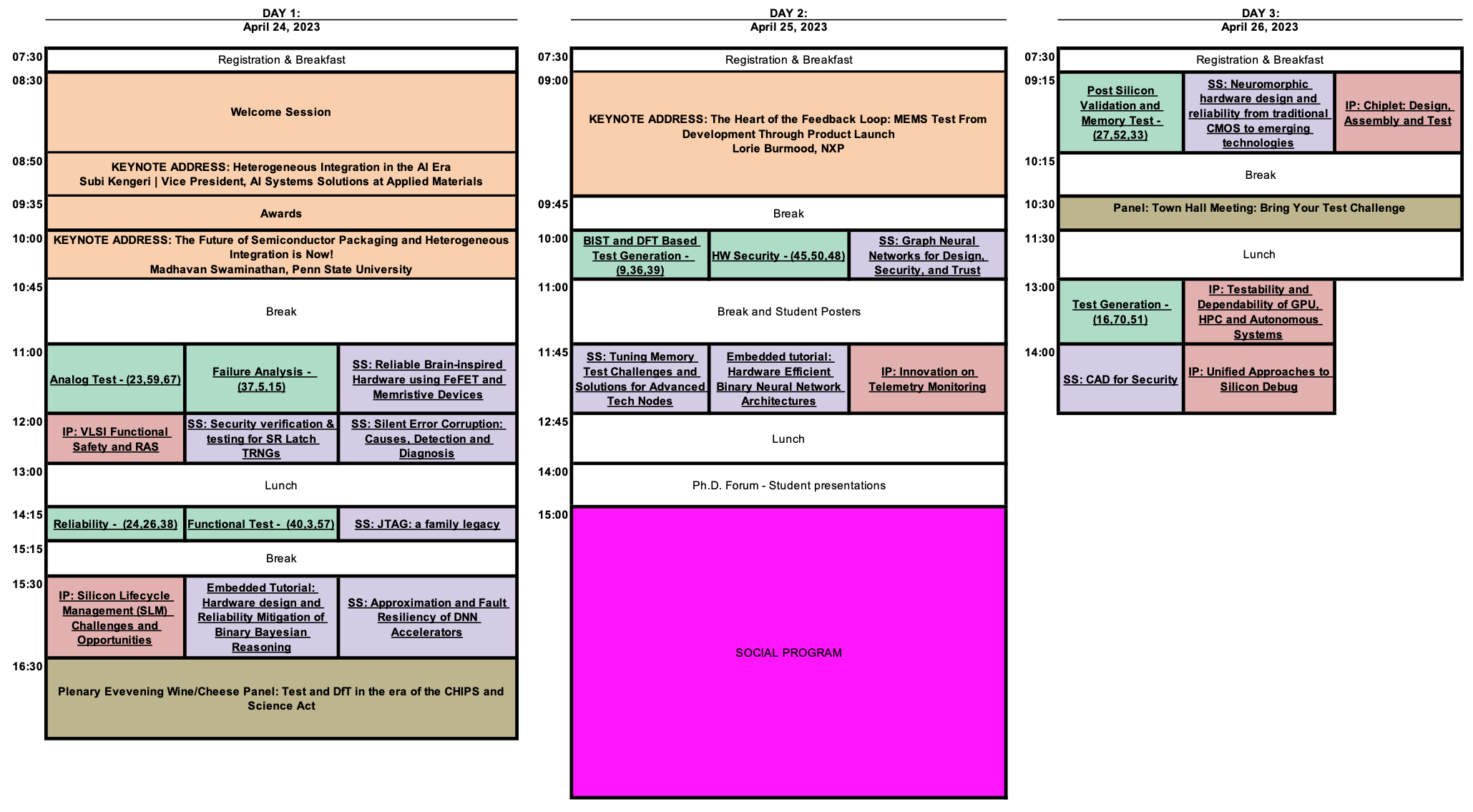

Program at a glance

This year, VTS received a total of 80 regular scientific paper submissions, of which 22 were accepted for presentation, resulting in an acceptance rate of 27.5%

VTS 2023 technical program

08:50

Palm I/Palm II

KEYNOTE ADDRESS: Heterogeneous Integration in the AI Era

10:00

11:00

Belmont

Session 1A: Analog Test

Outlier Detection For Analog Tests Using Deep Learning Techniques

Speaker: Chin-Kuan Lin

Authors: Chin-Kuan Lin, Cheng-Che Lu, Shuo-Wen Chang, Ying-Hua CHU, Kai-Chiang Wu, Mango Chao

Machine Learning-Based Adaptive Outlier Detection For Underkill Reduction In Analog/RF IC Testing

Speaker: Vineeth Niranjan

Authors: Vineeth Niranjan, Deepika Neethirajan, Dallas Webster, Amit Nahar, Constantinos Xanthopoulos, Yiorgos Makris

Architectural Radiation Hardening Of CMOS Power Management Circuits Through Bias Tuning

Speaker: Gauri Koli

Authors: Gauri Koli, Liam Nguyen, Jennifer Kitchen

Palm I

Session 1B: Failure Analysis

Gerabaldi: A Temporal Simulator For Probabilistic IC Degradation And Failure Processes

Speaker: Ian Hill

Authors: Ian Hill, Andre Ivanov

Diagnosis Of Quantum Circuits In The NISQ Era

Speaker: Yen-Wei Li (National Taiwan University)

Authors: Yu-Min Li, Cheng-Yun Hsieh, Yen-Wei Li, Chien-Mo LI

Targeted Custom High-Voltage Stress Patterns on Automotive Designs

Speaker: Saidapet Ramesh

Authors: Saidapet Ramesh, Jaiswal Akshay, Marchese Robert, Thota Sunny, Dickson Kristofor

Palm II

Session 1C: SS: Reliable Brain-inspired Hardware using Classical and Emerging Memories

Reliability Modeling of Emerging FeFET Technology

Speaker: Hussam Amrouch (U Stuttgart)

Robust and Efficient BNNs on Emerging Hardware

Speaker: Jian-Jia Chen and Mikail Yayla (TU Dortmund)

Neuromorphic Hardware with Memristive Devices

Speaker: Ahmedullah Aziz (Tennessee Knoxville, USA)

12:00

Palm I

Session 2A: IP - VLSI Functional Safety and RAS

Safety Mechanisms for Transient faults in Automotive - cost vs. effectiveness Speaker: Meirav Nitzan (Qualcomm)

Fault injection for automotive functional safety Speaker: Presenter: Ankush Sethi (NXP)

Managing Intermittent and Degrading Faults through Advanced Sensors, Analytics and Predictive Maintenance Speaker: Dan Alexandrescu (Synopsys)

Palm II

Session 2B: SS - Security verification & testing for SR Latch TRNGs

In silicon validation of SR-latch TRNG

Speaker: Jean-Luc Danger (Telecom Paris)

The impact of aging on SR-latch TRNG

Speaker: Naghmeh Karimi (UMBC)

Health tests in various certification schemes (NIST SP 800 90B, AIS BSI 31, OSCCA GM/T 0078)

Speaker: Sylvain Guilley (Telecom Paris & Secure IC)

Belmont

Session 2C: SS - Silent Error Corruption: Causes, Detection and Diagnosis

A Perspective on Silent Data Error Sources

Speaker: Sreejit Chakravarty (Intel)

Detecting Timing Marginalities that Cause Silent Data Errors

Speaker: Adit Singh (Auburn U)

Silent Error Modeling and Measurement Across the Layers

Speaker: Dimitris Gizopoulos (U Athens)

14:15

Belmont

Session 3A: Reliability

A Novel Lbist Signature Computation Method For Automotive Microcontrollers Using A Digital Twin

Speaker: Leon Klimasch

Authors: Daniel Tille, Leon Klimasch, Sebastian Huhn

Vmin Prediction Using Nondestructive Stress-Test

Speaker:

Authors: Chun Chen, Jeng-Yu Liao, Chien-Mo Li, Harry Chen, Eric Jia-Wei Fang

Predicting The Silent Data Error Prone Devices Using Machine Learning

Speaker: Mohammad Ershad Shaik

Authors: Mohammad Ershad Shaik, Abhishek Kumar Mishra, Yonghyun Kim

Palm I

Session 3B: Functional Test

Functional Test Generation For AI Accelerators Using Bayesian Optimization

Speaker: Arjun Chaudhuri

Authors: Arjun Chaudhuri, Ching-Yuan Chen, Jonti Talukdar, Krishnendu Chakrabarty

Expanding A Pool Of Functional Test Sequences To Support Test Compaction

Speaker: Irith Pomeranz

Authors: Irith Pomeranz

A Guided Debugger-Based Fault Injection Methodology For Assessing Functional Test Programs

Speaker: Francesco Angione

Authors: Francesco Angione, Paolo Bernardi, Nicola DI Gruttola Giardino, Davide Appello, claudia Bertani, Vincenzo Tancorre

Palm II

Session 3C: SS - JTAG: a family legacy

Nine years after its release, what is the future for 1687 ?

Speaker: Martin Keim (Siemens)

New frontiers for JTAG: Analog, Interfaces and System

Speaker: Jeff Rearick (AMD)

IEEE Std 1149.1 is being revised - what to expect?

Speaker: Heiko Ehrenberg

15:30

Palm I

Session 4A: IP - Silicon Lifecycle Management Challenges and Opportunities

Silicon health monitoring for automotive predictive maintenance Speaker: Robert Jin (NXP)

Hardware/Software Infrastructure to enable Silicon Monitoring throughout the IC Lifecycle Speaker: Nilanjan Mukherjee (Mentor/Siemens)

The need for End-to-end SLM Highway Speaker: Yervant Zorian (Synopsys)

Palm II

Session 4B: Embedded Tutorial

Hardware design and Reliability Mitigation of Binary Bayesian Reasoning Speakers: Lorena Anghel (Grenoble INP) and Mehdi Tahoori (KIT)

Belmont

Session 4C: SS - Approximation and Fault Resiliency of DNN Accelerators

GPU-Accelerated Framework for DNN Approximation Exploration

Speaker: Alberto Bosio (INL - École Centrale de Lyon)

Harnessing Approximation for Fault Injection in DNN Accelerators

Speaker: Maksim Jenihhin (Tallinn University of Technology)

Fault resiliency in DNNs

Speaker: Ernesto Sanchez (Politecnico di Torino)

09:00

10:00

Belmont

Session 5A: BIST and DFT Based Test Generation

Fully Deterministic Storage Based Logic Built-In Self-Test

Speaker: Subashini Gopalsamy

Authors: Subashini Gopalsamy, Irith Pomeranz

Test Generation For Defect-Based Faults Of Scan Flip-Flops

Speaker: Yu-Teng Nien

Authors: Yu-Teng Nien, Chen-Hong Li, Pei-Yin Wu, Yung-Jheng Wang, Kai-Chiang Wu, Mango Chao

Design For Testability (DFT) For RSFQ Circuits

Speaker: Mingye Li

Authors: Mingye Li, Yunkun Lin, Sandeep Gupta

Palm I

Session 5B: HW Security

CAPEC: A Cellular Automata Guided FSM-Based IP Authentication Scheme

Speaker: Farimah Farahmandi

Authors: Mridha Md Mashahedur Rahman, Mohammad Rahman, Rasheed Kibria, Mike Borza, Bandi Reddy, Adam Cron, Fahim Rahman, Mark Tehranipoor, Farimah Farahmandi

A Low Overhead Checksum Technique For Error Correction In Memristive Crossbars For Deep Learning Applications

Speaker: Mehdi B Tahoori

Authors: Surendra Hemaram, Soyed Tuhin Ahmed, Mahta Mayahinia, Christopher Mãœnch, Mehdi Tahoori

Thwarting Reverse Engineering Attacks Through Keyless Logic Obfuscation

Speaker: Leon Li

Authors: Leon Li, Alex Orailoglu

Palm II

Session 5C: SS - Graph Neural Networks for Design, Security, and Trust

Fault Criticality-aware GNN Training on ReRAM-based Processing-in-Memory Systems

Speaker: Partha Pande (Washington State U)

Graph Neural Networks for Hardware Vulnerability Analysis - Can you Trust your GNN?

Speaker: Lilas Alrahis (NYUAD)

Using GNNs for Tier-Level Fault Localization in Monolithic 3D Ics

Speaker: Krishnendu Chakrabarty (ASU)

11:45

Belmont

Session 6A: SS - Tuning Memory Test Challenges and Solutions for Advanced Tech Nodes

An Efficient External Memory Test Solution: Case Study for HPC Application

Speaker: Gurgen Harutyunyan (Synopsys)

Authors: Keqing Ouyang (ZTE/Sanechips), Minqiang Peng (ZTE/Sanechips), Yunnong Zhu (ZTE/Sanechips), Kang Qi (ZTE/Sanechips), Grigor Tshagharyan (Synopsys), Arun Kumar (Synopsys), Gurgen Harutyunyan (Synopsys), Isaac Wang (Synopsys)

Allocating Physically Aware Embedded Memory Test & Repair Processor using Floorplan Info at the RTL Design Level

Speaker: Raj Chudasama

Authors: Vinay Kumar (Intel), Raj Chudasama (Intel), Bin BW Wang (Intel), Manish Arora (Synopsys), Bharath Shankaranarayanan (Synopsys)

Overcoming Embedded Memory Test & Repair Challenges in the Gate-All-Around Era

Speaker: Gurgen Harutyunyan

Authors: Artur Ghukasyan (Synopsys), Grigor Tshagharyan (Synopsys), Gurgen Harutyunyan (Synopsys), Yervant Zorian (Synopsys)

Palm II

Session 6B: Embedded Tutorial

Hardware Efficient Binary Neural Network Architectures

Speaker: Ahmet Enis Cetin (UIC)

Palm I

Session 6C: IP - Innovation on Telemetry Monitoring

Elevating Die-To-Die Interface Testing and Repair with On-die Diagnosis

Speaker: Marc Hutner (ProteanTecs)

Application of On-Chip Monitors to Improve Quality and Functional Safety

Speaker: Chen He (NXP)

How Silicon Observability Enables Prescriptive Maintenance

Speaker: Sashi Obilisetty (Synopsys)

09:15

Belmont

Session 7A: Post Silicon Validation and Memory Test

Kernel Smoothing Technique Based On Multiple-Coordinate System For Screening Potential Failures In NAND Flash Memory

Speaker: Gooyoung Kim

Authors: Gooyoung Kim, Youngseon Moon, Jongmin Kim

Pre And Post Silicon Server Platform Transient Performance Using Trans-Inductor Voltage Regulator

Speaker: Ritchie Rice (Intel)

Authors: Judy Amanor-Boadu, Rishik Bazaz, Ritchie Rice, Azizi Shuma, Horthense Tamdem

Auxiliary State-Machine Controlled Autonomous Design Verification Framework

Speaker: Navaneeth Kumar (TI)

Authors: Gurumurti Avhad, Navaneeth Kumar, Shitin Sahu

Spiking Neural Networks accelerators in traditional CMOS technologies

Speaker: Alessio Carpegna

Augmented silicon photonics platforms for neuromorphic accelerators

Speaker: Fabio Pavanello

Design and Reliability Considerations of Emerging Memory-based SNNs

Speaker: Stefano Di Carlo

Palm I

Session 7C: IP - Chiplet: Design, Assembly and Test

The New Open Chiplet Economy Speaker: Bapi Vinnakota (Lawrence Berkeley Labs)

Multi-Die Stack Assembly and Interconnects Speaker: Jaber Derakhshandeh (IMEC)

Standardizing Chiplet Interconnect Test Speaker: Sreejit Chakravarty (Intel)

13:00

Palm II

Session 8A: Test Generation

Effective And Efficient Testing Of Large Numbers Of Inter-Die Interconnects In Chiplet-Based Multi-Die Packages

Speaker: Po-Yao Chuang (NTHU / imec / Cadence)

Authors: Po-Yao Chuang, Francesco Lorenzelli, Sreejit Chakravarty, Cheng-Wen Wu, Georges Gielen, Erik Jan Marinissen

An Exploration Of ATPG Methods For Redacted Ip And Reconfigurable Hardware

Speaker: Jackson Fugate

Authors: Greg Stitt, Naren Vikram Raj Masna, Venkata Kalluru, Swarup Bhunia, Nij Dorairaj, David Kehlet

Compact Set Of Functional Broadside Tests With Fault Detection On Primary Outputs

Speaker: Irith Pomeranz

Authors: Irith Pomeranz

Palm I

Session 8B: IP - Testability and Dependability of GPU, HPC and Autonomous Systems

AWPERA: ATPG-Aware Observation Point Insertion using Graph Convolutional Networks Speaker: Arjun Chaudhuri (nVidia)

Application-Driven Target Setting, Fault Impact and High-Performance Computing and Machine Learning Resiliency

Speaker: Michael Paulitsch (Intel)

The safety challenges of deploying autonomous vehicles - from the chip perspective

Speaker: Eric Zhang (Untether AI)

14:00

Palm II

Session 9A: SS - CAD for Security

SoC Security Verification: Challenges and Solutions

Speaker: Farimah Farahmandi (UFL)

Harnessing pre-silicon simulation to detect and root-cause side-channel leakage

Speaker: Nicole Fern, Jasper van Woudenberg, or Rajesh Velegalati

An Intermediate Representation for Hardware Security Verification

Speaker: Ryan Kastner (UC SanDiego)

Palm I

Session 9B: IP - Unified Approaches to Silicon Debug

Scan and Embedded Memory State Extraction for Silicon Debug, Validation, and Analysis Speaker: Mike Ricchetti (Synopsys)

Platform-level observability of SoC Scan and Array Functional states for System and In-Field Debug Speaker: Sankaran Menon (Intel)

Use-cases and ROI for unified verification, test and silicon debug sequences using Design-for-Verification Speaker: David Akselrod (AMD)