Tuesday, April 23

Registration and Breakfast

Time: 07:30 – 09:00

Plenary: Welcome session

Room: Pebble

Time: 09:00 – 09:20

- Welcome from the General Chair

Chen-Huan Chiang (Intel)Presenter - Program highlights

Stefano Di Carlo (Politecnico di Torino) and Peilin Song (IBM)Presenter

Keynote: Quantum Computation with Noisy intermediate-scale quantum (NISQ) processors

Room: Pebble

Time: 09:20 – 10:05

Moderator: Peilin Song (IBM)

Presenter: Abhinav Kandala (IBM)

Abstract: The development of noisy, intermediate-scale quantum computers has raised the possibility of addressing problems that are intractable with classical computation, even in the absence of quantum error correction. In this talk, I shall present a brief overview of superconducting quantum technology at IBM, and discuss metrics to benchmark the performance of NISQ processors. I shall then discuss our experimental implementations of hybrid quantum-classical algorithms on these systems, and demonstrate that the accuracy of these computations is largely limited by decoherence. I shall then introduce an error mitigation technique to obtain zero-noise estimates of expectation values, that requires no additional quantum resources, and is therefore readily accessible to NISQ hardware. These techniques have great applicability to a range of computations, extending the computational reach of noisy quantum processors.

Plenary: Awards Cerinomy

Room: Pebble

Time: 10:05 – 10:15

- Awards Cerimony

Moderator: Stefano Di Carlo (Politecnico di Torino)

Presenter: Dr. Patrick Groeneveld (Stanford University)

Abstract: The advanced technology that drives the next generation of vehicles will be presented. Building up from Newtonian physics and electrical engineering we will analyze motor efficiency, reliability, safety, performance and manufacturing cost. By comparing that to gasoline-powered cars we can present a unique science-based foundation for a sound economical and environmental transportation policy. For a fact-based bigger picture we will derive the full well-to-wheel cost emissions and other impacts of all propulsion options. We will show that the results are much more nuanced than the polarized information from either side of the political debate on climate change.

Break

Time: 11:00 – 11:20

1A – Regular Session: Analog and Mixed Signal

Room: Pebble

Time: 11:20 – 12:20

Moderator: Haruo Kobayashi (Gumma University)

- An Accurate and Efficient Method for Eliminating the Requirement of Coherent Sampling in Multi-Tone Test

Cheng Ban, Minshun Wu, Jiangtao Xu, Li Geng (Xi’an Jiaotong University), Degang Chen (Iowa State University)Presenter - Machine Learning-based Noise Classification and Decomposition in RF Transceivers

Deepika NeethirajanPresenter, Constantinos Xanthopoulos, Kiruba Subramani (UT Dallas), Keith Schaub, Ira Leventhal (Advantest America, Inc.), Yiorgos Makris (UT Dallas) - Online Millimeter Wave Phased Array Calibration Based on Channel Estimation

Thomas MoonPresenter, Junfeng Guan, Haitham Hassanieh (University of Illinois)

1B – New Topic: Emerging Computing and Testing Techniques

Room: Beach

Time: 11:20 – 12:20

Organizer & Moderator: Bozena Kaminska (Simon Fraser University) & Bernard Courtois (BC Consulting)

Abstract: Continuing a tradition at the IEEE VLSI Test Symposium this new topic session presents two interesting talks on new emerging computing and testing techniques. The first talk focuses on carbon nanotube electronics while the second talk discusses about wafer level testing under magnetic field.

- CNT Computing

Max Shulaker (MIT)Presenter - Wafer Level Testing Under Magnetic Field

Laurent Lebrun (Hprobe)Presenter

1C – Regular Session: Test Standards and Scan Test

Room: Pacific

Time: 11:20 – 12:20

Moderator: Sandeep Gupta (University of Southern California)

- A Graph Theory Approach Towards IJTAG Security via Controlled Scan Chain Isolation

Abhishek DasPresenter, Nur Touba (University of Texas at Austin) - Efficient Structured Scan Patterns Retargeting for Hierarchical IEEE 1687 Networks

Ahmed Ibrahim (University of Twente)Presenter, Abrar Ibrahim, Mona SAFAR, El-Kharashi M. Watheq (Ain Shams University), Hans Kerkhoff (University of Twente) - A Novel Graph Coloring Based Solution for Low-Power Scan Shift

Saurabh GuptaPresenter, Bonita Bhaskaran, Shantanu Sarangi, Ayub Abdollahian (Nvidia Corp.), Jennifer Dworka (Southern Methodist University)

Lunch

Time: 12:20 – 13:30

2A – Regular Session: Delay & Performance Test

Room: Pebble

Time: 13:30 – 14:30

Moderator: Murali Venkatasubramanian (Intel)

- Automatic Test Pattern Generation (ATPG) for timing verification and delay testing of RSFQ circuits

Fangzhou WangPresenter, Sandeep Gupta (University of Southern California) - Path Delay Test of the Carnegie Mellon Logic Characterization Vehicle

Benjamin Niewenhuis (Carnegie Mellon University), Balaji Ravikumar (PES University), Zeye Liu, Shawn Blanton (Carnegie Mellon Univ.)Presenter - Test Compaction Under Bounded Transparent-Scan

Irith Pomeranz (Purdue University)Presenter

2B – Hot Topic: In-System-Test (IST) Architecture for NVIDIA Drive-AGX Platforms

Room: Beach

Time: 13:30 – 14:30

Organizer: Pavan Datla (NVIDIA Corp.)

Moderator: Saurabh Gupta (NVIDIA Corp.)

Abstract: Safety is one of the crucial features of autonomous drive platforms, and semiconductor chips used in these architectures must guarantee functional safety aspects mandated by ISO 26262 standard. This special session discusses the in-system-test (IST) architecture and solutions that helps with achieving highest functional safety levels on the NVIDIA Drive-AGX platforms.

- High Level Overview of the NVIDIA Automotive Platform and the In-System Test Architecture

Pavan Kumar Datla JagannadhaPresenter, Mahmut Yilmaz, Milind Sonawane, Sailendra Chadalavada, Shantanu Sarangi, Bonita Bhaskaran, Shashank Bajpai, Venkat Abilash Reddy, Jayesh Pandey, Sam Jiang (NVIDIA Corp.) - Practical Solutions to Implementation Challenges

Pavan Kumar Datla Jagannadha, Mahmut Yilmaz, Milind SonawanePresenter, Sailendra Chadalavada, Shantanu Sarangi, Bonita Bhaskaran, Shashank Bajpai, Venkat Abilash Reddy, Jayesh Pandey, Sam Jiang (NVIDIA Corp.)

2C – Regular Session: 2.5D, 3D and SiP Test

Room: Pacific

Time: 13:30 – 14:30

Moderator: T.M. Mak (Independent)

- A Comparative Study of Prebond TSV Test Methodologies

Sourav DasPresenter, Fei Su, Sreejit Chakravarty (Intel Corporation) - Test-Cost Reduction for 2.5D ICs Using Microspring Technology for Die Attachment and Rework

Zhanwei Zhong (Duke University)Presenter, Tom B. Wrigglesworth, Eugene Chow (Palo Alto Research Center), Krishnendu Chakrabarty (Duke University) - Reliable Power Delivery and Analysis of Power-Supply Noise During Testing in Monolithic 3D ICs

Abhishek Koneru (Duke University), Aida Todri-Sanial (CNRS-LIRMM), Krishnendu Chakrabarty (Duke University)Presenter

Break

Time: 14:30 – 15:00

3A – Regular Session: Best papers from the China Test Conference

Room: Pebble

Time: 15:00 – 16:00

Moderator: Xiaowei Li (ICT, Chinese Academy of Sciences)

- Leveraging Memory PUFs and PIM-based encryption to secure edge deep learning systems

Wen LiPresenter, Ying Wang, Huawei Li, Xiaowei Li (Institute of Computing Technology, CAS) - Novel Application of Deep Learning for Adaptive Testing Based on Long Short-Term Memory

Tai SongPresenter, Huaguo Liang (Heifei University of Technology), Ying Sun (PingDingShan Industrial college of Technology), Zhengfeng Huang; Maoxiang Yi, Xiangsheng Fang (Heifei University of Technology), Aibin Yan (Anhui University) - ZeroScreen: A Novel Structure for IC Reliability Screening at Time-Zero

Liting YuPresenter, Xiaoxiao Wang (Beihang University)

3B – Hot Topic: Countering IP Security Threats in Supply Chain

Room: Beach

Time: 15:00 – 16:00

Organizer & Moderator: Naghmeh Karimi (University of Maryland, Baltimore County)

Abstract: The continuing decrease in feature size of integrated circuits, and the increase of the complexity and cost of design and

fabrication has led to outsourcing the design and fabrication of integrated circuits to third parties across the globe, and in turn

has introduced several security vulnerabilities. This special session discusses these security threats in the supply chain and the state-of-the-art countermeasures to tackle such threats.

fabrication has led to outsourcing the design and fabrication of integrated circuits to third parties across the globe, and in turn

has introduced several security vulnerabilities. This special session discusses these security threats in the supply chain and the state-of-the-art countermeasures to tackle such threats.

- Learn & Churn: A Knowledge Guided Approach to Hardware IP Trust Assurance

Swarup Bhunia (University of Florida)Presenter - Frequently Asked Questions on Strip-Functionality Logic Locking

Jeyavijayan (JV) Rajendran (Texas A&M University)Presenter - IP Security Threats and Hardware Trojans

Hassan Salmani (Howard University)Presenter

3C – IP Session: Machine Learning Applications in IC

Test-Related Tasks

Room: Pacific

Time: 15:00 – 16:00

Organizer: Haralampos Stratigopoulos (Sorbonne University, CNRS, LIP6)

Moderator: Yiorgos Makris (UT Dallas)

Abstract: Over the last decade there has been a surge of activity in employing advanced statistical analysis and machine learning methods to various test-related tasks. The topic is no longer simply a matter of academic curiosity but, rather, a pressing need of the industry as it seeks to address various challenges. In this session, three industry experts have been invited to give their perspective, describe machine learning use cases, and discuss challenges and future work ideas. The three talks will cover the use of deep learning for hotspot detection, the challenge of rendering machine learning-based decisions in the semiconductor industry trustable and explainable, and data analytics across the complete product cycle towards improved product reliability.

- Using Deep Learning to Detect, Understand and Resolve Hotspots in the Design Stage

Kareem MADKOUR (Mentor, A Siemens Business)Presenter - Trustable AI for Dependable Systems

Ira LEVENTHAL (Advantest)Presenter - Data Driven Telecom Product Reliability

Xinli Gu (HUAWEI)Presenter

Break

Time: 16:00 – 16:30

PLENARY – Wine and cheese: AI-powered Security Validation and Test

Room: Pebble

Time: 16:30 – 18:00

Organizer: Farimah Farahmandi and Mark Tehranipoor (University of Florida)

Moderator: Farimah Farahmandi (University of Florida)

Abstract: Artificial Intelligence (AI) is becoming an integral part of our daily lives. AI is also becoming a major component for test community, cyber-security community, manufacturing, Internet-of-Things, and more. AI may be able to analyze test data, yield analysis, penetration test, fuzzy test, and negative test to extract vulnerabilities and defects. However, there may be a limited control on what AI systems learn and policies they internalize in their learning process. AI learns a task through objective functions. Defining objective functions to reflect security concerns and verification is of high importance. If objective function does not cover all aspects of security requirements and the correct functionality, there is a chance that AI learns vastly different concepts and ends up in unwanted situations. Further, AI may internalize some sensitive information which is decodable by reverse engineering. The panelists will address a number of issues in this emerging and inter-disciplinary field.

- Presenters:

- Iris Ma (Enflame)

- Mark Tehranipoor (University of Florida)

- Rob Aitken (ARM)

- Sohrab Aftabjahani (Intel)

- Yiorgos Makris (UT-Dallas)

TPC Meeting (By invitation only)

Time: 18:30 – 20:30

Wednesday, April 24

Registration and Breakfast

Time: 07:30 – 08:30

4A – Regular Session: Embedded Systems & Board Test

Room: Pebble

Time: 08:30 – 09:30

Moderator: Marco Restifo (Politecnico di Torino)

- Black-Box Test-Coverage Analysis and Test-Cost Reduction Based on a Bayesian Network Model

Renjian Pan (Duke University)Presenter, Zhaobo Zhang (Huawei Technologies), Xin Li, Krishnendu Chakrabarty (Duke University), Xinli Gu (Huawei Tech., Inc.) - Optimized Stress Testing for Flexible Hybrid Electronics Designs

Hang Gao, Umit Ogras, Ganapati Bhat, Sule Ozev (Arizona State University) - Board-Level Functional Fault Identification using Streaming Data

Mengyun Liu (Duke University)Presenter, Fangming Ye (Huawei Tech., Inc.), Xin Li, Krishnendu Chakrabarty (Duke University), Xinli Gu (Huawei Tech., Inc.)

4B – Embedded Tutorial: Reliability of Hardware-Implemented Spiking Neural Networks (SNN)

Room: Beach

Time: 08:30 – 09:30

Organizer: Ioana Vatajelu (TIMA Laboratory), Lorena Anghel (University of Grenoble-Alpes / TIMA Laboratory), Giorgio Di Natale (TIMA Laboratory)

Moderator: Huawei Li (Chienes Academy of Science)

Abstract: This Embedded Tutorial is dedicated to the recent advances related to the analysis and optimization of fault-tolerance characteristic of hardware-implemented Spiking Neural Networks, with special emphasis on circuits designed using nonvolatile emerging memory technologies.

- Fundamentals of Spiking Neural Networks, Fault Modelling & Fault Injection

Lorena AnghelPresenter, Giorgio Di Natale (TIMA Laboratory)Presenter - Fault Tolerance Assessment and Optimisation Methods

Elena-Ioana Vatajelu (TIMA Laboratory)Presenter

4C – IP Session: IEEE 1687.xyz

Room: Pacific

Time: 08:30 – 09:30

Organizer: Jeff Rearick (AMD)

Moderator: Jeff Rearick (Advanced Micro Devices)

Abstract: The IEEE 1687-2014 standard introduced the concept of portable, retargetable tests for digital circuits and taught how to apply them via a JTAG Test Access Port. Two follow-on standardization efforts address the topics of portable, retargetable analog tests (IEEE P1687.2) and applying analog or digital tests via non-TAP interfaces (IEEE P1687.1). IEEE P2427 complements these efforts by defining how to measure and report coverage of analog tests. This IP session will use a running example to show how all three initiatives play together.

- Using IEEE P1687.2 to write and apply analog tests

Jeff Rearick (Advanced Micro Devices)Presenter - Using IEEE P1687.1 to retarget tests to non-TAP interfaces

Alfred Crouch (Amida Technology Solutions)Presenter - Using IEEE P2427 to measure the coverage of analog tests

Hans Martin Von Staudt (Dialog Semiconductor)Presenter

Break

Time: 09:30 – 09:45

5A – Regular Session: Design Verification, Validation and Diagnosis

Room: Pebble

Time: 09:45 – 10:45

Moderator: Patrick Girard (LIRMM / CNRS)

- Mixed Signal Design Validation Using Reinforcement Learning Guided Stimulus Generation for Behavior Discovery

Barry Muldrey (Georgia Institute of Technology), Suvadeep Banerjee (Intel Corporation), Abhijit Chatterjee (Georgia Institute of Technology)Presenter - Silicon Proven Timing Signoff Methodology using Hazard-Free Robust Path Delay Tests

Ankit ShahPresenter, Raman Nayyar, Arani Sinha (Intel Corp.) - Observation Point Placement for Improved Logic Diagnosis based on Large Sets of Candidate Faults

Irith Pomeranz (Purdue University)Presenter, Vivek Chickermane (Cadence Design Systems), Srikanth Venkataraman (Intel Corporation)

5B – Embedded Tutorial: A Quality and Reliability Driven DFT and DFR Strategy for Automotive and Industrial Markets

Room: Beach

Time: 09:45 – 10:45

Organizer: Scott Martin, Malav Shah (Texas Instruments)

Moderator: Vivek Chickermane (Cadence)

Abstract:

- A Quality and Reliability Driven DFT and DFR Strategy for Automotive and Industrial Markets

Malav Shah, Scott Martin, Subhadeep Ghosh

(Texas Instruments)

5C – IP Session: Design for Test in State-of-the-Art Analog Systems

Room: Pacific

Time: 09:45 – 10:45

Organizer & Moderator: Jennifer Kitchen (Arizona State University)

Abstract: There is a growing demand for low-cost and effective test solutions to support state-of-the-art analog and mixed-signal systems that are continuously increasing in complexity and functionality, while decreasing in product cost. This innovative practice session highlights various aspects of design for test (DfT) in high-complexity, analog-dominated systems with three talks that focus on: DfT in power management integrated circuits (ICs), an alternative testing method to analog test bus, and pre-silicon built-in self-test (BIST) verification, where BIST is used to monitor complex mixed-signal systems. These talks will be given by industry experts from Dialog Semiconductor, Xilinx, and Texas Instruments.

- The Power to Test: DfT Challenges for Testing Power Management ICs

Hans Martin von Staudt (Dialog Semiconductor)Presenter - Concurrent Sampling with Local Conversion: A Practical Alternative to Analog Test Bus

Amit Majumdar (Xilinx)Presenter - Pre-Silicon Analog & Mixed-Signal Verification of BIST Solutions for First-Pass Success

Ibukun Olumuyiwa Presenter, Lakshmanan Balasubramanian, Ashwini Padoor (Texas Instruments)

5D – Poster Session: TTTC ‘s E. J. McCluskey Doctoral Thesis Posters

Room: Grove

Time: 09:45 – 10:45

Organizer & Moderator: Naghmeh KARIMI (University of Maryland, Baltimore County)

The full list of the VTS19 Semifinalists is available here

Break

Time: 10:45 – 11:00

6A – Regular Session: In-System and Cell Aware Test

Room: Pebble

Time: 11:00 – 12:00

Moderator: Mango Chao (National Chiao Tung University)

- Hybrid Performance Modeling for Optimization of In-System-Structural-Test (ISST) Latency

Milind SonawanePresenter, Venkat Abilash Reddy Nerallapally, Alex Hsu, Shantanu Sarangi (NVIDIA Corp.) - Layout-Based Dual-Cell-Aware Tests

Tse-Wei Wu, Dong-Zhen LeePresenter, Kai-Chiang Wu, Yu-Hao Huang (National Chiao Tung University), Ying-Yen Chen, Po-Lin Chen, Mason Chern, Jih-Nung Lee, Shu-Yi Kao (Realtek Semiconductor Corp.), Mango Chao (National Chiao Tung University)

6B – Hot Topic: Photonic IC Testing – Challenges and Opportunities

Room: Beach

Time: 11:00 – 12:00

Organizer: Gary Evans (Southern Methodist University)

Moderator: Rob Aitken (ARM)

Abstract: Silicon photonics is a field of growing importance as the need for communication speed and bandwidth continues to increase dramatically. This special session will provide background on Silicon Photonics and the impact of silicon photonics on test through two talks by experts in the field.

- Silicon Photonics Technologies

Attila Mekis (Luxtera)Presenter - Silicon Photonics Testing: State-Of-The-Art, Challenges, and Future Requirements

Manoj NiraulaPresenter, Vipul Patel, Prakash Gothoskar (Cisco) - Optical Performance Characterization in a High-Volume Silicon Photonics Manufacturing Flow

Attila Mekis (Luxtera)Presenter

6C – IP Session: DFT for AI Chips

Room: Pacific

Time: 11:00 – 12:00

Organizer: Huang Yu (Mentor Graphics)

Moderator: Rahul Singhal(Mentor Graphics)

Abstract: Hardware acceleration for Artificial Intelligence (AI) is now a very competitive and rapidly evolving market. As a result, fast time-to-market is a leading concern for this segment. To speed up time-to-market and ensure quality, new design-for-test (DFT) architectures, new DFT methodologies and technologies are emerging. AI chips are typically very big with many identical and non- identical cores, distributed memories, high-speed IOs, which makes testing of such a gigantic SoC a very challenging task. We found it is very important for us to understand these new challenges from the point of views of DFT engineers. In this innovative practice session, we invited three DFT experts from three AI chip companies to share their experiences of DFT on AI chips.

- Deep Dive into Test for AI SoCs

Iris MA (Enflame, China)Presenter - DFT for AI Chips – The Graphcore Experience

Hui King Lau (Graphcore)Presenter - DFT and IP Core Test Considerations for an AI System-in-Package Device

Joe Reynick (eSilicon)Presenter

Lunch

Time: 12:00 – 13:30

7A – Regular Session: On-Line Test & Error Correction

Room: Pebble

Time: 13:30 – 14:30

Moderator: Maria Michael (University of Cyprus)

- Defective pixel analysis for Image sensor online diagnostic and self-healing

Ghislain Takam TchendjouPresenter, Emmanuel Simeu (TIMA Laboratory) - Layered-ECC: A Class of Double Error Correcting Codes for High Density Memory Systems

Abhishek DasPresenter, Nur Touba (University of Texas at Austin) - Cache Design for Yield-per-Area Maximization

Soowang ParkPresenter, Sandeep Gupta (University of Southern California)

7B – Hot Topic: Does Approximation Make Testing Harder (or Easier)?

Room: Beach

Time: 13:30 – 14:30

Organizer & Moderator: Iris Bahar (Brown University)

Abstract: Many important application domains, including machine learning, feature intrinsically noise tolerant algorithms. While this may translate into relaxed constraints for testing and verification of approximate systems, distinguishing actual design bugs from what is being approximated also becomes harder. In this special session, using representative case studies, we pose several challenges for the test and verification community as approximate computing becomes more prevalent as a design of choice.

- Catching Design Bugs under Approximation

Ulya R. Karpuzcu (University of Minnesota)Presenter - Testing of Approximate Software

Sasa Misailovic (University of Illinois at Urbana-Champaign)Presenter - Managing Approximation with Hardware Transactional Memory

R. Iris Bahar (Brown University)Presenter

7C – IP Session: In-system Test and Reliability of Memories

Room: Pacific

Time: 13:30 – 14:30

Organizer: Gurgen Harutyunyan (Synopsys)

Moderator: Grigor Tshagharyan (Synopsys)

Abstract: This innovative practice session includes three presentations which discuss test and reliability issues and solutions for external and embedded memories. At speed test for external memories, memory array diagnosis and interconnect faults detection, as well as the peculiarities of supporting different memory IPs including DRAM and HBM2 are among the topics discussed. As for embedded memories, FIT rate calculation and mitigation methodology is presented which is shown to be critical for automotive SoCs.

- Efficient Infrastructure for External Memory DRAM Test

Jayanth Mekkoth (Cisco), S. Bandyopadhyay (Cisco), A. Kumar (Synopsys) - Testing HBM2 in At-Speed Mode

Marc Hutner (Teradyne)Presenter, G. Tshagharyan (Synopsys), G. Harutyunyan (Synopsys) - FIT Rate Calculation and Mitigation Methodology for Memories in Automotive SoCs

G. Boschi (Intel), H. Shaheen (Intel), D. Luongo (Intel), D. Lazzarotti (Intel), H. Grigoryan (Synopsys), G. Harutyunyan (Synopsys), S. Shoukourian (Synopsys), Yervant Zorian (Synopsys)Presenter

Break

Time: 14:30 – 15:00

Social Program

Time: 15:00 – 21:00

Thursday, April 25

Registration and Breakfast

Time: 07:30 – 08:30

8A – Regular Session: Learning Based Diagnosis, Test and Security

Room: Pebble

Time: 08:30 – 09:30

Moderator: Spencer Millican (Auburn University)

- Diagnosis Outcome Preview through Learning

Chenlei FangPresenter, Qicheng Huang, Soumya Mittal, Shawn Blanton (Carnegie Mellon Univ.) - Wafer Pattern Recognition Using Tucker Decomposition

Ahmed Wahba (UC Santa Barbara)Presenter, Nik Sumikawa (NXP Semiconductors), Zheng Zhang, Li-C. Wang (UC Santa Barbara) - Analog Performance Locking through Neural Network-Based Biasing

Georgios VolanisPresenter, Yichuan Lu, Sai Govinda Rao Nimmalapudi, Angelos Antonopoulos, Andrew Marshall, Yiorgos Makris (UT Dallas)

8B – Special session: TTTC ‘s E. J. McCluskey Doctoral Thesis Award 1

Room: Beach

Time: 08:30 – 09:30

Organizer & Moderator: Naghmeh Karimi (University of Maryland, Baltimore County)

The full list of the VTS19 Semifinalists is available here

8C – IP Session: Innovate Practices on CyberSecurity of Hardware Semiconductor Devices

Room: Pacific

Time: 08:30 – 09:30

Organizer: Alfred Crouch (Amida Technology Solutions)

Moderator: Muhammad Yasin (Texas A&M University)

Abstract: The term CyberSecurity means many different things to many people — some think of data security, some think of identity protection, some think of intrusion attacks on the internet or USB ports. In reality, CyberSecurity represents any type of attack on computing machines and one of the attacks that is often overlooked is attacks by the supply chain to inject malfeasant circuitry into semiconductor devices as they are made. This is the one aspect of Design-for-Security and Design-for-Trust that is often overlooked. This IP session will propose three talks on CyberSecurity from both industry and academia.

- Using Embedded Instruments to Facilitate Machine Learning for Trojan Hunting

Alfred Crouch (Amida Technology Solutions)Presenter - Fixing the Leaks in Insecure Circuits

Jennifer Dworak (Southern Methodist University)Presenter - Novel IC Sub-Threshold IDDQ Signature and Its Application to Hardware Security

Franco Stellari, Naigang Wang, Peilin Song (IBM Watson Research Center)Presenter

Break

Time: 09:30 – 09:45

9A – Regular Session: Hardware Security 1

Room: Pebble

Time: 09:45 – 10:45

Moderator: Giorgio Di Natale (TIMA – CNRS / Université Grenoble-Alpes / Grenoble INP)

- Quality Obfuscation for Reliable and Adaptive Hardware IP Protection

Abdulrahman Alaql, Tamzidul HoquePresenter, Domenic Forte, Swarup Bhunia (University of Florida) - PCB Hardware Trojans: Attack Modes and Detection Strategies

Matthew McGuire, Umit Ogras, Sule Ozev (Arizona State University) - RTL-PSC: Automated Power Side-Channel Leakage Assessment at Register-Transfer Level

Miao He, Jungmin ParkPresenter, Adib Nahiyan (University of Florida), Aposto Vassilev (National Institute of Standards and Technology), Yier Jin, Mark Tehranipoor (University of Florida)

9B – Special session: TTTC ‘s E. J. McCluskey Doctoral Thesis Award 2

Room: Beach

Time: 09:45 – 10:45

Organizer & Moderator: Naghmeh Karimi (University of Maryland, Baltimore County)

The full list of the VTS19 Semifinalists is available here

9C – IP Session: Innovative Test Practices in Japan

Room: Pacific

Time: 09:45 – 10:45

Organizer: Hauro Kobayashi (Gunma University)

Moderator: Kazumi Hatayama (Gunma University / Evaluto)

Abstract: The IP session highlights three innovative test practices in Japan, which include DC parametric test time reduction using digital controlled DC resource and deep reconsideration for ADC distortion testing as well as test time reduction of low sampling rate and high resolution ADC linearity. These would be useful for automotive and IoT application device testing.

- Dynamic Distortion of ADCs:Its Recognition and Acquisition

Yuji Gendai (THine Electronics)Presenter - Techniques for Reducing DC Parametric Test Time Based on a Digitally Controlled DC Resource

Yusuke AsadaPresenter, Takahiko Shimizu (Advantest Corporation) - An FFT-based INL Prediction Methodology for Low Sampling Rate and High Resolution Analog-to-Digital Converter

Keno SatoPresenter, Takashi Ishida, Toshiyuki Okamoto, Tamotsu Ichikawa (Rohm Semiconductor), Jiang-Lin Wei, Nene Kushita, Hirotaka Arai, Anna Kuwana, Takayuki Nakatani, Kazumi Hatayama, Haruo Kobayashi (Gunma University)

Break

Time: 10:45 – 11:00

10A – Regular Session: Hardware Security 2

Room: Pebble

Time: 11:00 – 12:00

Moderator: Ujjwal Guin (Auburn University )

- A Secure and Low-overhead Active IC Metering Scheme

Aijiao Cui, Yan Yang (Harbin Institute of Technology), Gang Qu (University of Maryland)Presenter, Huawei Li (Chinese Academy of Sciences) - Hardware-based Real-time Workload Forensics via Frame-based TLB Profiling

Yunjie ZhangPresenter, Liwei Zhou, Yiorgos Makris (UT Dallas) - Shielding Logic Locking from Redundancy Attacks

Leon LiPresenter, Alex Orailoglu (University of California at San Diego)

10B – Panel: Automotive Functional Safety: DFT, Verification, Emulation?

Room: Beach

Time: 11:00 – 12:00

Organizer & Moderator: Anshuman Chandra (Synopsys)

Abstract: Functional safety has emerged as the number one consideration when designing solutions for automotive industry. Automotive embedded design is witnessing exponential increase in complexity and product variety. This is primarily driven by the personalized products and high-tech solutions for safety and comfort demanded by the customers, regulators and stringent standards put in place. This panel will discuss the implications of automotive functional safety requirements on all aspects of the SOC design, manufacturing quality and particularly in-system functional safety with respect to the role of design-for test (DFT), functional verification and emulation. The panel will further discuss the range solutions for different categories of automotive SOCs.

- Presenters:

- Srinivas Patil (Qualcomm)

- Meirav Nitzan (Synopsys)

- Shah, Malav (Texas Instruments)

10C – IP Session: Automotive Test

Room: Pacific

Time: 11:00 – 12:00

Organizer: Peter Sarson (Dialog Semiconductor)

Moderator: Elena-Ioana Vatajelu (TIMA Laboratory)

Abstract: In this IP session, there will be 2 presentations focusing on how to increase the in-field quality level of A/MS devices. The 1st presentation will discuss how to increase the observed return rates of Automotive ICs to 10ppb but at the same time as removing the costly burn in stage.

The 2nd presentation goes into detail of how to use a System Level Test to increase the reliability of an Automotive device, by adding a functional test to the flow of the test program.

The 2nd presentation goes into detail of how to use a System Level Test to increase the reliability of an Automotive device, by adding a functional test to the flow of the test program.

- Is it Possible to Produce a 10 PPB Automotive Circuit Without Burn-in?

Wim Dobbelaere (OnSemi)Presenter - Advanced and Effective System Level Test for Increasing Reliability of Automotive SoCs

Marco Restifo (Politecnico di Torino)Presenter

Lunch

Time: 12:00 – 13:30

11A – Regular Session: Test ATPG & Compression

Room: Pebble

Time: 13:30 – 14:30

Moderator: Alex Orailoglu (University of California at San Diego)

- A new method for software test data generation inspired by D-algorithm

Jianwei ZhangPresenter, William Halfond, Sandeep Gupta (University of Southern California) - An Incremental Automatic Test Pattern Generation Method for Multiple Stuck-at Faults

Peikun WangPresenter, Amir Masoud Gharehbaghi (The University of Tokyo), Masahiro Fujita (Univ. of Tokyo) - On Cyclic Scan Integrity Tests for EDT-based Compression

Jerzy Tyszer (Poznan University of Technology), Wu-Tung Cheng (Mentor Graphics Corporation), Grzegorz Mrugalski (Mentor Graphics), Janusz Rajski (Mentor Graphics Corporation)Presenter, Maciej Trawka (Gdynia Maritime University)

11B – Embedded Tutorial: Delay Fault Testing: Present and Future

Room: Beach

Time: 13:30 – 14:30

Organizer: Vishwani Agraval (Auburn University)

Moderator: Xiaowei Li (ICT, Chinese Academy of Sciences)

Abstract: This embedded tutorial presents a brief survey of digital delay fault testing, which lists 100+ references on fault models, simulators, ATPG, DFT, and tools. Continuing studies are needed in this maturing field for new technologies, signal integrity, process variations, faster than critical path operation, asynchronous circuits, counterfeit ICs, and hardware Trojans. This information is compiled to provide direction to students, practicing engineers, and researchers alike.

- Delay Fault Testing: Present and Future

Jubayer Mahmod, Spencer MillicanPresenter, Ujjwal Guin, Vishwani Agrawal (Auburn University)

11C – IP Session: Software and Hardware based Silicon Debug / Fault Isolation

Room: Pacific

Time: 13:30 – 14:30

Organizer & Moderator: Amit Jakati (Globalfoundries)

Abstract: Achieving quicker product yield ramp depends on how quickly manufacturing defects and their underlying root causes are identified, specifically the systematic ones. The IP session discusses the concepts, challenges, and opportunities of semiconductor yields and industry-proven methodologies that improve yield of digital semiconductor products using machine learning based analysis of volume scan test diagnosis results. We also discuss what it takes to set-up and perform successful hardware based non-destructive fault isolation on wafer and packaged (modules) parts. The packed modules add a layer of complexity with respect to cooling and backside sample preparation.

- What Is Yield Learning? The Role Of Diagnosis In Yield Analysis

Manish Sharma (Mentor)Presenter - Advanced Wafer Level Non-destructive Fault Isolation (FI) and Challenges

Amit Jakati (Globalfoundries)Presenter - More Challenges: Fault Isolation on Packaged Parts, EFA-DFT Methodology and Workflow

Joy Liao (NVIDIA)Presenter

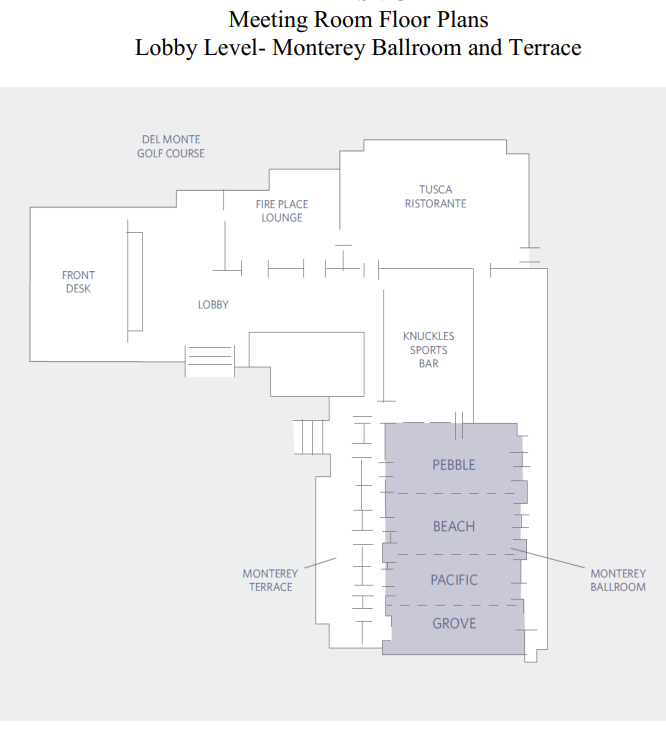

Check the floor plan

Check the floor plan