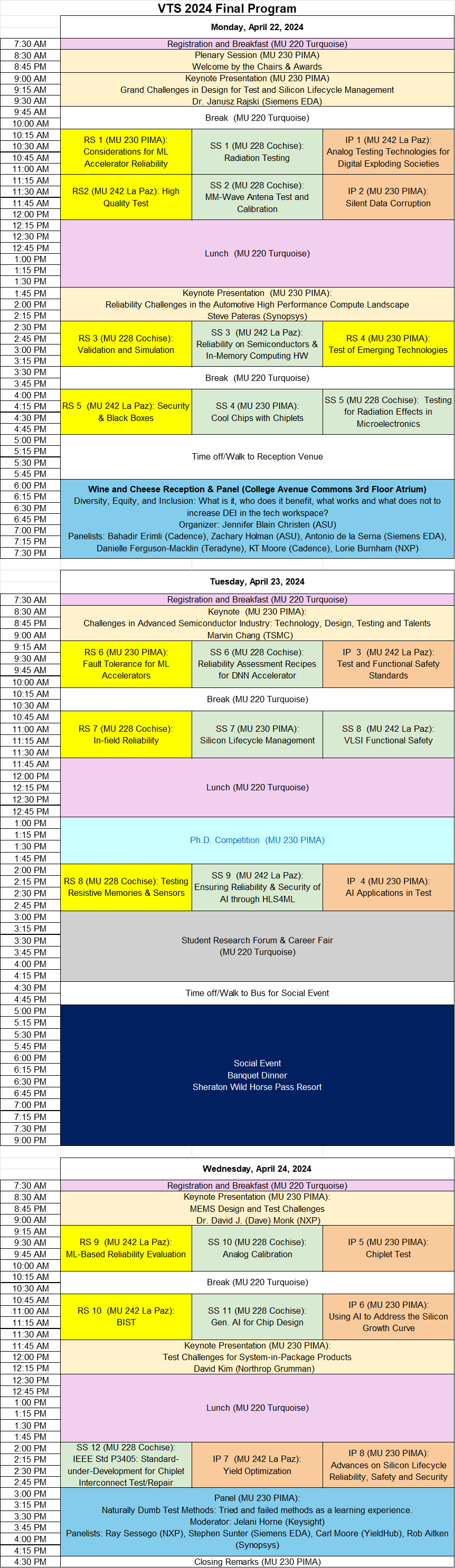

Registration desk will be open

- Mon 7:30AM-3PM

- Tues 7:30AM-2PM

- Wednesday 7:30AM-12PM

VTS 2024 Final Program

09:00

10:15

Regular Session 1: Considerations for ML Accelerator Reliability (MU 230 PIMA)

Analyzing and Mitigating Circuit Aging

Effects in Deep Learning Accelerators

Speaker: Sanjay DAS

Authors: Sanjay DAS,

Shamik KUNDU,

Anand MENON (University of Texas at Dallas),

Shubha KHAREL,

Yihui REN (Brookhaven National Laboratory),

Kanad BASU (University of Texas at Dallas)

On the Sensitivity of Analog Artificial

Neural Network Models to Process Variation

Speaker: Yiorgos MAKRIS

Authors: Nosheen AFROZ,

Ahmad Sayeed SAYEM,

Georgios VOLANIS (UT Dallas),

Dzmitry MALIUK (Yale University),

Haralampos STRATIGOPOULOS (Sorbonne Univ., CNRS, LIP6),

Yiorgos MAKRIS (UT Dallas)

Analyzing the Impact of Scheduling Policies

on the Reliability of GPUs running CNN operations

Speaker: Robert LIMAS SIERRA

Authors: Robert LIMAS SIERRA,

Francesco PESSIA,

Juan GUERRERO,

Josie RODRIGUEZ CONDIA,

Matteo SONZA REORDA (Politecnico di Torino)

Special Session 1: Radiation Testing (MU 228 Cochise)

Session Chair: Adalin Benedetto (Alphacore Inc)

Total Ionizing Dose Radiation Effects - Mechanisms and Test Structure Design

Speaker: Hugh Barnaby (ASU)

Single Event Effects - Mechanisms and Test Structure Design

Speaker: Daniel Loveless (UTC)

Radiation Hardness Assurance Testing

Speaker: Gregory R Allen (JPL)

IP Session 1: Analog Testing Technologies for Digital Exploding Societies (MU 242 La Paz)

Session Chair: Haruo Kobayashi (Gunma University)

Development of 13fsrms Low Jitter 1GHz Crystal Oscillator for ATE Reference Clock

Speaker: Naoki Tsukahara (Advantest)

Sub-ns Testing Using SAR Time-to-Digital Converter

Speaker: Keno Sato (ROHM Semiconductor)

ADC Diagnosis by Exploiting LMS Digital Calibration

Speaker: Takashi Oshima (Hitachi Ltd)

11:15

Regular Session 2: High Quality Test (MU 242 La Paz)

Customizing ATPG User-Defined Stresses and

Tests To Target Cell-Neighborhood-Bridging Defects

Speaker: Stephen TRAYNOR

Authors: Stephen TRAYNOR (NXP),

Saidapet RAMESH,

Lawrence HERR,

Maryfe HERNANDEZ,

Scott CHEN (NXP Semiconductors)

Test Compaction Using (k,1)-Cycle Tests

Speaker: Irith POMERANZ

Authors: Irith POMERANZ (Purdue University)

Scenario-based Test Content Optimization:

Scan-Test vs. System-Level Test

Speaker: Nourhan ELHAMAWY

Authors: Nourhan ELHAMAWY,

Jens ANDERS,

Ilia POLIAN (University of Stuttgart),

Matthias SAUER (Advantest)

Special Session 2: mm-Wave Antena Test and Calibration (MU 228 Cochise)

Session Chair: Jennifer Kitchen (ASU)

Characterization of Millimeter-wave Reconfigurable Intelligent Surfaces Using a Near-Field Measurement Setup

Speaker: Aditya Shekhawat (ASU)

Millimeter-wave and THz Measurement Practices

Speaker: Saeed Zeinolabedinzadeh (ASU)

Rapid measurements of Antenna-in-Package (AiP) scaling from mmWave to Sub-THz

Speaker: Christian Muresan (NI/Emerson)

Multi-Parameter Optimization of mm-Wave Antenna Layout Using Hybrid Modeling and Incremental Model Learning

Speaker: Ferhat Can Ataman (ASU)

IP Session 2: Silent Data Corruption (MU 230 PIMA)

Session Chair: Adit Singh (Auburn U)

‘Si’lent Data Errors – Detection and Resilience

Speaker: Shubhada Sahasrabudhe (Intel)

Addressing Silent Data Corruption Challenges

Speaker: Yervant Zorian (Synopsys)

13:45

14:30

Regular Session 3: Validation and Simulation (MU 228 Cochise)

A Method for Simulating Mixed-Signal ATE Tests

Speaker: Stephen SUNTER

Authors: Stephen SUNTER (Siemens Digital Industries Software),

Vladimir ZIVKOVIC (Infineon),

Bartlomiej PRASELSKI (Siemens Digital Industries Software)

Testing a Transistor-Level Programmable Fabric: Challenges and Solutions

Speaker: Apurva JAIN

Authors: Apurva JAIN,

Thomas BROADFOOT,

Carl SECHEN (The University of Texas at Dallas),

Yiorgos MAKRIS (UT Dallas)

Logic-AAA: Debug of Logic Failures with an on-ATE Expert System

Speaker: Chris NIGH

Authors: Chris NIGH (Carnegie Mellon University),

Shawn BLANTON (Carnegie Mellon Univ., Pittsburgh, USA)

Special Session 3: Reliability on Semiconductors & In-Memory Computing Hardware (MU 242 La Paz)

Session Chair: Daphne Chen (ASU)

From the Invisible to the Indispensable: Nitrogen-Vacancy Magnetometry for Higher Yield and Reliability in Semiconductors

Speaker: Umberto Celano (ASU)

Empowering analog computing with high precision

Speaker: Wenhao Song (USC)

A Test Platform for Characterizing Emerging Nonvolatile Memories for Computing

Speaker: Matthew Marinella (ASU)

Practical Considerations on ESD Testing

Speaker: Albert Wang (UCR)

Regular Session 4: Test of Emerging Technologies (MU 230 PIMA)

Characterization of 14nm CMOS Technology At Cryogenic Temperatures Using Dense Addressable Arrays

Speaker: Raphael ROBERTAZZI

Authors: Raphael ROBERTAZZI,

David FRANK,

John TIMMERWILKE,

Kevin TIEN (IBM Research),

Peilin SONG (IBM Corp.),

Daniel FRIEDMAN (IBM Research)

Reliability analysis and mitigation for analog computation-in-memory: from technology to application

Speaker: Mahta MAYAHINIA

Authors: Mahta MAYAHINIA (KIT university),

Haneen G. HEZAYYIN,

Mehdi TAHOORI (Karlsruhe Institute of Technology)

16:00

Regular Session 5: Security & Black Boxes (MU 242 La Paz)

Fuzz Wars: The Voltage Awakens - Voltage-Guided Blackbox Fuzzing on FPGAs

Speaker: Jonas KRAUTTER

Authors: Kai SU (Karlsruhe University of Applied Sciences),

Mark Leon GIRAUD (Fraunhofer IOSB),

Anne BORCHERDING (Fraunhofer Institute of Optronics, System Technologies and Image Exploitation IOSB),

Jonas KRAUTTER (Karlsruhe Institute of Technology, Germany),

Philipp NENNINGER (Karlsruhe University of Applied Sciences),

Mehdi TAHOORI (Karlsruhe Institute of Technology)

A Novel Self-referencing Approach Using Memory Power-up States for Detecting COTS SRAMs

Speaker: Zakia Tamanna TISHA

Authors: Gaines ODOM,

Zakia Tamanna TISHA,

Ujjwal GUIN (Auburn University)

Static Gate-Level Information Flow for Hardware Information Security with Bounded Model Checking

Speaker: Jiaji HE

Authors: Yiqiang ZHAO,

Gongsen QU,

Qizhi ZHANG,

Yao LI,

Zhengyang LI,

Jiaji HE (Tianjin University)

Special Session 4: Cool Chips with Chiplets (MU 230 PIMA)

Session Chair: Leslie Hwang (ASU)

Thermal Modeling and Management Challenges in Heterogenous Integration: 2.5D Chiplet Platforms and Beyond

Speaker: Umit Ogras (UWisc)

Reliable Network-on-Interposer Design for CNN Inferencing in Presence of Defective Chiplets

Speaker: Partha Pande (WSU)

Overcoming Communication Bottlenecks in Scale-out Machine Learning with Silicon Photonic 2.5D Interposer Networks

Speaker: Sudeep Pasricha (CSU)

Special Session 5: Testing for Radiation Effects in Microelectronics (MU 228 Cochise)

Session Chair: Andrew Levy (Alphacore)

Total Ionizing Dose Testing of Alphacore’s ADC with ASU’s Cobalt-60 GammaCell

Speaker: Adalin Benedetto (Alphacore)

Test Methods for Total Ionizing Dose Effects on Capacitors

Speaker: Chandru Ramamurthy (Alphacore)

Neutron Single Event Characterization and Simulation Fidelity for a CCD Imager

Speaker: Merritt Miller (Fifth Gait)

18:00

Wine and Cheese Reception & Panel (College Avenue Commons 3rd Floor Atrium)

Diversity, Equity, and Inclusion: What is it, who does it benefit, what works and what does not to increase DEI in the tech workspace?

Moderator: Jennifer Blain Christen (ASU)

Panelists: Bahadir Erimli (Cadence),

Zachary Holman (ASU),

Antonio de la Serna (Siemens EDA),

Danielle Ferguson-Macklin (Teradyne),

KT Moore (Cadence),

Lorie Burmood (NXP)

08:30

09:15

Regular Session 6: Fault Tolerance for ML Accelerators (MU 230 PIMA)

Error Resilient Hyperdimensional Computing Using Hypervector Encoding and Cross-Clustering

Speaker: Mohamed MEJRI

Authors: Mohamed MEJRI, Chandramouli AMARNATH, Abhijit CHATTERJEE (Georgia Institute of Technology)

Drop-Connect as a Fault-Tolerance Approach for RRAM-based Deep Neural Network Accelerators

Speaker: Mingyuan XIANG

Authors: Mingyuan XIANG, Xuhan XIE (Univeristy of Chicago),

Pedro SAVARESE (TTI-Chicago), Xin YUAN (Univeristy of Chicago),

Michael MAIRE, Yanjing LI (University of Chicago)

NN-ECC: Embedding Error Correction Codes in Neural Network Weight Memories using Multi-task Learning

Speaker: Surendra HEMARAM

Authors: Soyed Tuhin AHMED, Surendra HEMARAM, Mehdi TAHOORI (Karlsruhe Institute of Technology)

Special Session 6: Reliability Assessment Recipes for DNN Accelerators (MU 228 Cochise)

Session Chair: Seth Abraham (ASU)

Hybrid Analytical and Hierarchical FI-based Reliability Assessment for Systolic-Array-Based DNN Accelerators

Speaker: Maksim Jenihhin (TalTech, Estonia)

Mixing techniques for the Reliability Assessment of in-chip AI accelerators in GPUs

Speaker: Josie Esteban RODRIGUEZ CONDIA ( POLITO, Italy)

Reliability Assessment of DNN Hardware Accelerators through Physical Fault Injection”

Speaker: Fernandes DOS SANTOS (INRIA, France)

IP Session 3: Test and Functional Safety Standards (MU 242 La Paz)

Session Chair: Arani Sinha (Intel)

What can I expect from the refresh of IEEE 1687?

Speaker: Martin Keim (Siemens-EDA)

P2427 analog defect modeling, improved by 967 ballot comments

Speaker: Steve Sunter (Siemens-EDA)

IEEE P2851.1 - The standardization initiative for the enablement of functional safety interoperability with reliability

Speaker: Jyotika Athavale (Synopsys)

10:45

Regular Session 7: In-field Reliability (MU 228 Cochise)

Sequential Decoders for Binary Linear Block ECCs

Speaker: Valentin GHERMAN

Authors: Valentin GHERMAN, Cyrille LAFFOND (CEA LIST)

Temperature-Insensitive Soft-Error-Tolerant Flip-Flop Design For Automotive Electronics

Speaker: Yen-Ju SU

Authors: Ralf E.-H. YEE, Yen-Ju SU, Lowry P.-T. WANG, Charles H.-P. WEN,

Herming CHIUEH (National Yang Ming Chiao Tung University)

Enhanced Wear-Out Sensor Design in a 12nm Process for Separable Stress Regime Monitoring

Speaker: Ian HILL

Authors: Ian HILL, Mateo RENDóN, Andre IVANOV (University of British Columbia)

Special Session 7: Silicon Lifecycle Management (MU 230 PIMA)

Session Chair:

Addressing the Combined Effect of Transistor and Interconnect Aging in SRAM Towards Silicon Lifecycle Management

Speaker: Mehdi Tahoori (Karlsruhe Institute of Technology)

An Efficient Lifecycle Test & Repair Infrastructure for Addressing Lifetime-Induced Faults in CAMs

Speaker: Bhrugurajsinh Chudasama (Intel)

Advanced SLM Sensors for Monitoring Degradation of Emerging Memories

Speaker: Fabian Vargas (IHP Microelectronics)

Special Session 8: VLSI Functional Safety (MU 242 La Paz)

Session Chair: Jim Plusquellic (UNM)

Automotive Requirements from a Semiconductor Perspective

Speaker: Mahesh Kumarasamy (Samsung)

Unified Functional Safety Framework for Advanced Multi-domain SoCs combining ISO26262 & IEC 61508

Speaker: Gulroz Singh (NXP)

Functional Safety landscape for IPs

Speaker: Ankush Sethi (NXP)

13:00

Ph.D. Competition (MU 230 PIMA)

- Ishaan Bassi - Arizona State University

- Md Toufiq Hasan Anik - University of Maryland

- Shamik Kundu - UT Dallas

- Vineeth Amritur Niranjan - University of Texas at Dallas

- Zain Ul Abideen - Carnegie Mellon University

- Ahmed Abed Benbük - Arizona State University

- Shao-Chun Hung - Duke University

14:00

Regular Session 8: Testing Resistive Memories & Sensors (MU 228 Cochise)

Calibration and Source Localization Using an Array of Resistive Metal Oxide Gas Sensors

Speaker: Ishaan BASSI

Authors: Ishaan BASSI, Sule OZEV (Arizona State University)

Multi-Level Reference for Test Coverage Enhancement of Resistive-Based NVM

Speaker: Sina BAKHTAVARI MAMAGHANI

Authors: Sina BAKHTAVARI MAMAGHANI (Karlsruhe Institute of Technology),

Jongsin YUN, Martin KEIM (Siemens Digital Industries Software), Mehdi TAHOORI (Karlsruhe Institute of Technology)

Testing and Fault Diagnosis for Multi-level Resistive Random-Access Memory in Monolithic 3D Integration

Speaker: Shao-Chun HUNG

Authors: Shao-Chun HUNG (Duke Unicersity), Partho BHOUMIK, Krishnendu CHAKRABARTY (Arizona State University)

Special Session 9: Ensuring Reliability & Security of AI through HLS4ML (MU 242 La Paz)

Session Chair:

AIN Sputtering Parameter Estimation Using A Multichannel Parallel DCT Neural Network

Speaker: Ahmet Enis Cetin (UIC)

A High Level Synthesis

Methodology for Dynamic Monitoring of FPGA

ML Accelerators

Speaker: Seda Ogrenci (NWU)

Reliable edge machine learning hardware for

scientific applications

Speaker: Nhan Tran (Fermilab)

IP Session 4: AI applications in test (MU 230 PIMA)

Session Chair: Stefano Di Carlo (Politecnico di Torino)

AI In Test: Applications of Traditional ML and GenAI for Product Development

Speaker: Abhijit Sathaye (Intel)

Optimizing manufacturing test in volume production

Speaker: Sashi Obilisetty (Synopsys)

AI Era Semiconductor Testing: AI/ML Use Cases from Wafer to System-Level Testing

Speaker: Keith Schaub (Advantest)

08:30

Keynote Presentation: MEMS Design and Test Challenges (MU 230 PIMA)

09:15

Regular Session 9: ML-Based Reliability Evaluation (MU 242 La Paz)

Evaluating the Reliability of Supervised Compression for Split Computing

Speaker: Juan GUERRERO

Authors: Juan GUERRERO, Josie RODRIGUEZ CONDIA (Politecnico di Torino),

Marco LEVORATO (University of California Irvine), Matteo SONZA REORDA (Politecnico di Torino)

Transformer and Its Variants for Identifying Good Dice in Bad Neighborhoods

Speaker: Cheng-Che LU

Authors: Cheng-Che LU, Chi-Chih CHANG, Chia-Heng YEN (National Yang Ming Chiao Tung University),

Shuo-Wen CHANG, Ying-Hua CHU (Qualcomm Inc.), Kai-Chiang WU, Mango CHAO (National Chiao Tung University)

WaferCap: Open Classification of Wafer Map Patterns using Deep Capsule Network

Speaker: Abhishek Kumar MISHRA

Authors: Abhishek Kumar MISHRA (Drexel University), Mohammad Ershad SHAIK (The University of Texas at Austin),

Anush LINGAMOORTHY, Suman KUMAR, Anup Kumar DAS, Nagarajan KANDASAMY (Drexel University), Nur TOUBA (University of Texas at Austin)

Special Session 10: Analog Calibration (MU 228 Cochise)

Session Chair: Bertan Bakkaloglu (ASU)

Machine Learning Based Static and Dynamic Error Calibration in Data Converters

Speaker: Arindam Sanyal (ASU)

Power-up Self Auto Calibration of High Speed SAR Converter in a 22nm FD-SOI CMOS Process

Speaker: Ahmet Tekin (Bogazici Univeristy)

High Precision Adaptive Calibration Feedback in RF Front-end for Digital Pre-distortion Application

Speaker: Emre Ulusoy (TUBITAK BILGEM)

PArtificial Intelligence Based High Power Calibration Method for RF Pulse Amplifiers

Speaker: A. Eroglu

IP Session 5: Chiplet Interconnect Test and Repair (MU 230 PIMA)

Session Chair: Sreejit Chakravarty (Ampere Computing)

Challenges of Chiplet Interconnect Test and Repair and where Standardization will help

Speaker: Pradipta Ghosh (Microsoft)

Silicon health management for multi-die systems

Speaker: Yervant Zorian (Synopsys)

Introducing IEEE P3405 and the chiplet interconnect test and repair standardization effort

Speaker: Sreejit Chakravarty (Ampere Computing)

10:45

Regular Session 10: BIST (MU 242 La Paz)

A Storage Based LBIST Scheme for Logic Diagnosis

Speaker: Subashini GOPALSAMY

Authors: Subashini GOPALSAMY, Irith POMERANZ (Purdue University)

Built in self test for RSFQ circuit

Speaker: Mingye LI

Authors: Mingye LI, Yunkun LIN, Sandeep GUPTA (University of Southern California)

Structural Built In Self Test of Analog Circuits using ON/OFF Keying and Delay Monitors

Speaker: Suhas KRISHNA KASHYAP

Authors: Suhas KRISHNA KASHYAP (Arizona state university),

Chinmaye RAGHAVENDRA (Arizona State University),

Suriyaprakash NATARAJAN (Intel Corporation), Sule OZEV (Arizona State University)

Special Session 11: Gen. AI for Chip Design (MU 228 Cochise)

Session Chair: Jeff Zhang (ASU)

ChipeNeMo: Domain-Adapted LLM for Chip Design

Speaker: Mingjie Liu (NVIDIA)

CircuitOps and OpenROAD: An Infrastructure for ML EDA Research and Education

Speaker: Vidya Chhabria (ASU)

LLMs for Hardware Design and Security: Boon or Bane

Speaker: Jeyavijayan "JV" Rajendran (TAMU)

LLMs and Foundation Models for Chip Design: The Good, the Backdoors and the Ugly

Speaker: Siddharth Garg (NYU)

IP Session 6: Using AI to Address the Silicon Growth Curve (MU 230 PIMA)

Session Chair: Duane Brown (Advantest)

Leveraging AI/ML to Design, Manufacture, and Test Advanced AI/ML Chips

Speaker: Ira Leventhal (Advantest)

AI For Test Optimization Early in Design Phase for Reduction in Test Patterns and Design Schedules

Speaker: Sri Ganta (Synopsys)

Revolutionizing Semiconductor Testing: The Fusion of LLMs like GPT-4 and Human Expertise

Speaker: Keith Schaub (Advantest)

11:45

Keynote Presentation: Test Challenges for System-in-Package Products (MU 230 PIMA)

14:00

Session Chair: Saket Kumar Goyal (Broadcom)

Analysis of Multi-Chiplet Package Designs & Requirements for Production Test Simplification

Speaker: Mike Kelly (Amkor Technology USA)

Chiplet Interconnect Repair Logic Description with Google’s Protocol Buffers

Speaker: Po-Yao Chuang and Erik Jan Marinissen (IMEC)

How IEEE Std P3405 Enables EDA Interoperability

Speaker: Martin Keim (Siemens)

IP Session 7: Yield Optimization (MU 242 La Paz)

Session Chair: Carl Moore (YieldHub)

Information is key to yield improvement

Speaker: Carl Moore (YieldHub)

Sustainable Yield Improvement

Speaker: John O'Donnell (YieldHub)

Test Hardware Design

Speaker: Jory Twitchell (NXP)

IP Session 8: Advances on Silicon Lifecycle Reliability, Safety and Security (MU 230 PIMA)

Session Chair: Sashi Obilisetty (Synopsys)

Addressing In-Field Dependability Challenges with SLM

Speaker: Jyotika Athavale (Synopsys)

Leveraging deep data analytics at test for lifetime reliability, performance and safety

Speaker: Zohaib Khan (ProteanTecs)

Scalable Physical Attacks on chips

Speaker: Marc Witteman (Riscure)

15:00

Panel: Naturally Dumb Test Methods: Tried and failed methods as a learning experience (MU 230 PIMA)

Moderator: Jelani Horne (Keysight) Panelists: Ray Sessego (NXP)

Stephen Sunter (Siemens EDA)

Carl Moore (YieldHub)

Rob Aitken (Synopsys)